- Featured in:

-

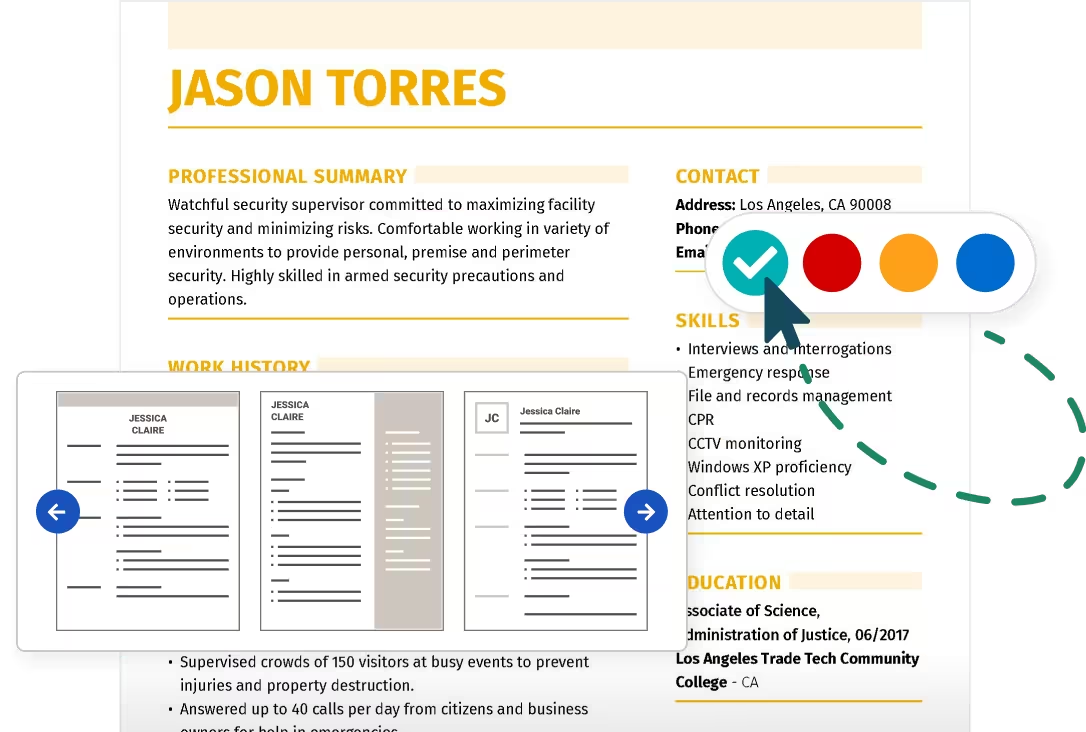

Find out what is the best resume for you in our Ultimate Resume Format Guide.

Additional Engineering Resume Samples

Fpga Engineer Resume Samples

No results found

6-10 years of experience

- Implemented a rapid development graphical VHDL workflow. Workflow includes Clearcase, HDL Designer, Synplify Pro and LutM fpga technology. Robust FPGA server peripherals include DDR1, DDR2, QDR2 and serdes resources.

- Authored complex game changing spatial-temporal image processing algorithms using Matlab.

- Translated game changing algorithms into fpga firmware for real time implementation.

- Provided consultation to mitigate printed wire board μV EMI problems with proper return current layout.

0-5 years of experience

Developed an RTL code for a Graphics Controller.

- Completed RTL Code Development in VHDL, and Validation of the design for a Video Display section.

- Integrated a Model of the IDT Dual Port Sram in the Test Bench – design was synthesized for a Vertex II Pro.

- Participated in all design reviews for the Bd.

0-5 years of experience

Designed and implemented 70G Ethernet Switch FPGA centric hardware solutions for a $70 million Carrier Ethernet Edge solutions company.

- Created Verilog PCIe Endpoint design to provide remote processor access to main fabric and daughter board memory mapped interfaces.

- Designed Verilog data path counter feature for 70G Ethernet platform. This module maintained 128K 64Bit counters.

- Created Nios embedded processor Verilog design to implement a Multilink PPP design.

- Designed and tested Verilog Ethernet SOAM functions in Carrier Ethernet products.

- Used System Verilog and UVM to test and verify complex FPGA(s).

- Integrated, tested, and verified HW/SW in lab using 10G test equipment and FPGA embedded logic analyzer.

0-5 years of experience

Contractor for Parker Aerospace, Altera FPGA Target

- Managed multiple verification engineers regarding testcase specification and mapping to verification vectors, responsible for reporting and progress

- Re-wrote full system uncompliant requirements for DO-254 with another engineer, accepted as compliant by Federal Designated Engineering Representative

- Focus on verification of two FPGA designs for Embraer Executive Jet flight control targeting Cyclone 3 FPGA

- Verified requirements using ModelSim Questa using VHDL and proprietary DO-254 verification system

- Verification included protocol, control/status registers, pipeline buffers and state machines

- Participated and organized formal HRS and HDD reviews recorded for FAA approval

0-5 years of experience

Coordinated every aspects of engineering design and development of Achieva’s products, 1G/2G Fiber Channel Controller and 4G Fiber Channel Controllers right from architecture and specs finalization to ASIC tape-out. Responsible for complete ASIC development and deliverables, right from architecture and specs finalization to ASIC bring-up. Also responsible for leading Software.

- Architected, Designed, verified and Single handedly developed the 1G/2G Fiber Channel Controller, which provides 1G/2G Fibre channel FC-1 and FC-2 layer functions. Fibre Channel Controller is a single chip storage area network solution for host bus adapters with full Fibre channel support.

- Responsible for complete IP development and deliverables, right from architecture and specs finalization to FPGA proto-type targeted on Xilinx Virtex-II Pro, including Architecture, Functional Specs Documentation, Architecture documentation, RTL design doc, Micro-architecture, RTL, STA, Simulations, Synthesis, and bring-up.

- Achieved success in releasing deliverables while meeting time, cost, scope, and quality.

- Established Design process and Methodology for development of Fiber Channel MACs.

- Successfully architected Fiber Channel MAC.

- Substantial hands-on contributions to the product with direct ownership of various architectural, implementation, and ongoing support issues.

- Strong hands-on experience in RTL coding using Verilog HDL, STA, DFT/ATPG, Synthesis, Simulations, and Lab testing.

- Successfully managed concurrent multi-projects and experienced in multi-tasking.

- Managed remote/overseas (India) engineering teams.

0-5 years of experience

- Created Radar Direction Finding application in Xilinx FPGA

- Added PPC405 support in Xilinx FPGA to support real-time analysis of Radar environment

- Supported legacy FPGA that analyzed Radar characteristics, such as pulse width, frequency and I&Q

0-5 years of experience

Contributed to developing control logic for a traffic manager using 3 Xilinx Vertex 5 FPGAs in VHDL

- Also developed a similar design in 2 Xilinx Virtex 6 FPGAs

- Frequently worked across organization to solve issues and develop features

- Used ModelSim/QuestaSim, Xilinx ISE and EDK for development tools

- Worked closely with Xilinx support staff to resolve tool problems

- Developed automated build system for FPGAs

- Made many architectural decisions after boss was promoted

- Was assigned routinely the most difficult issues because of having the most system

- Often wrote low level drivers in C for FPGA

- Was primarily responsible for reviewing resumes, doing phone and in person interviews for hiring a new entry level employee

0-5 years of experience

Designed, integrated, verified FPGA designs on multiple projects employing best design practices. Developed and maintained requirements using DOORs.

- Prepared bids for multiple FPGA proposals.

- Lead engineer for Universal Processor Manager utilizing five FPGAs managing a team of engineers.

- Integrated Synopsys USB core into three ASIC System On Chip designs. Verified design using Synopsys Verification IP.

0-5 years of experience

Participated to design and verify 3 different High Speed Digital ASICs/FPGAs for Gigabit Subsystem, which handled different kind of Network Protocols including TCP/IP.

- Participated with Product Line Management Team to generate the Architecture Document for Gigabit Subsystems.

- Wrote the Micro-Architecture Documents, SystemVerilog RTL Design and Block Level Verification the PCIe/PCI/USB DMA and Transmit FIFO Controllers Modules.

- Participated with Verification Team to generate Testcases and Debugging Chip Top Level.

- Participated with Validation Team to implement and debug the FPGAs version of Gigabit Subsystems.

- ASICs/FPGAs Lab Bring-Up and Debugging.

0-5 years of experience

FPGA technical lead for a custom beam-forming smart-antenna product intended for cellular networks.

- Responsible for high-level product architecture, software-hardware interface definition, FPGA design architecture, part selection, and FPGA design implementation leading a team of 3 design engineers.

- Involved in DSP system design using MATLAB with a specific focus on hardware-optimized multi-rate filter designs.

- Implemented CPRI interface leveraging Lattice IP core.

- Implemented Ethernet MAC and HDLC MAC layer functionality leveraging Lattice IP cores.

- Implemented multi-rate interpolation and decimation filters and NCOs in FPGA.

0-5 years of experience

Developed ASICs for IBOC used in HD Radio products. Responsibilities included validation of subsystems by developing system level tests written in C and Verilog run in simulation and FPGA. Aided board level tests by porting custom Windows software to the Linux environment for downloading firmware onto development boards.

- Validated system peripheral protocols including SPI, I2C, and I2S buses over AHB/APB.

- Verified JTAG, scan chain, and On-Chip Debug functionality of Tensilica HIFI and Vectra cores.

- Created software libraries for low-level access to hardware.

0-5 years of experience

Lead hardware engineer architecting and designing Software Defined Radios to be used in small satellites and CubeSats, for commercial and military customers. Designs involved development ARM processors, DSPs and FPGAs optimized for extremely small form factors and low power consumption.

- Developed all digital hardware and support equipment for a MUOS (military version of 3G cellphone) using Xilinx Zynq SoC including Gigabit Ethernet, DDR3L, HS USB, SPI, IIC and microSD

- Responsible for all FPGA development and support for narrowband and wideband waveforms

- Architected next generation single board radio to provide narrow and wideband communications, with highly customizable configurations to tailor performance or power consumption to specific applications

0-5 years of experience

Lead embedded hardware and FPGA engineer; hired and guided senior and new engineers

- Designed MPC855T and MPC80 hardware to SDRAM, FLASH, DSP and analog peripherals

- All layout, purchasing and manufacturing support to get alpha prototypes built and running

- FPGA design in Distributed Logic of a real-time, pipelined 19-bit x 4-bit + 5 bit signed offset

0-5 years of experience

Designed Digital Board and corresponding on 5K gate FPGA composed of 8 bit, shift register, corresponding look-up table, and data detector

- Hand coded FPGA Design in VHDL (5K Gates @ 21.5MHz), using Modelsim and Synopsys to compile, debug, simulate and synthesize code

- Performed Board Electrical Design using Mentor Design Architect.

- Board Design: Receive a serial data stream, clock, and enable from the Host, decode command data and send a corresponding tuning command to Phased-Locked Loops, Band Pass Filter Bank, and Phase-Locked Loop selector.

- Design and Presentation Applications: PowerPoint and Visio to create schematics, hardware design and specification documents and present design milestones.

0-5 years of experience

- Design, simulate, debug and test Xilinx FPGAs for low power, miniature spectrometers.

- FPGAs interface to high speed A2D, bar code reader/detector, SPI interface, internal and external FIFOs.

- Responsible for generating design specifications and requirements, data sheets, testing procedures, and all steps to release to production.

- Interface with customers, sales, marketing, and applications engineering to provide timely support to ensure customer satisfaction.

- All FPGA code written in VHDL for Spartan 2 and 3 families using Xilinx Synthesis and Place and Route tools.

- Simulation performed with Aldec and Xilinx Chipscope used for in-circuit analysis.

0-5 years of experience

- Design Verilog and VHDL applications for digital signal processing in wireless Ethernet products

- Translate algorithms from Matlab scripts into functional HDL and optimize for speed and efficiency

- Collaborate with coworkers from multiple disciplines to integrate modules from a team of FPGA engineers, Motorola and Xilinx IP, and embedded software into one seamless application

- Create comprehensive testbenches to simulate HDL functionality with Cadence Incisive Enterprise Simulator and ensure optimal performance

- Build FPGA binaries for Virtex-7 with Xilinx Vivado and perform on-chip debugging with ChipScope