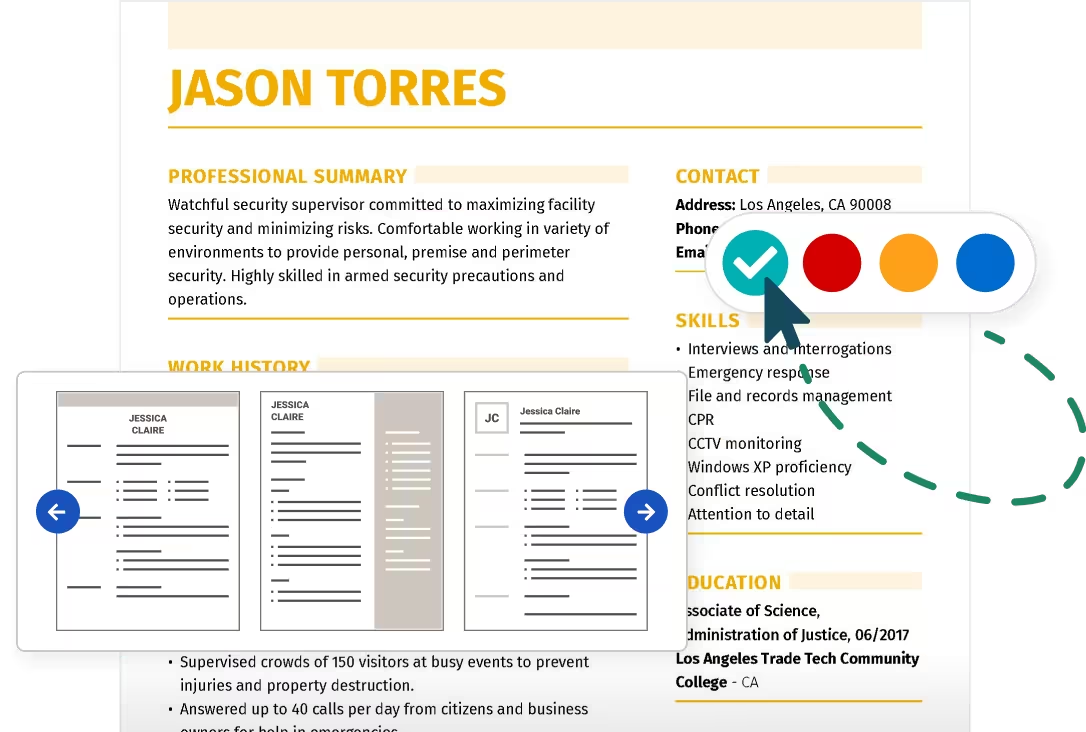

Find out what is the best resume for you in our Ultimate Resume Format Guide.

Additional Graphic Web Design Resume Samples

Digital Design Engineer Resume Samples

No results found

0-5 years of experience

Redesigned the image compression memory boards for the video teleconferencing market.

- Corrected a design flaw in a key product, completed the redesign in record time, saving over $300,000 a year in manufacturing costs.

- Designed the X.21 dual channel WAN telecommunications board containing a 68020 microprocessor and finite state machines. Developed test techniques, integrated hardware, firmware and system software and prepared first beta tests of the subsystem at customer sites.

- Directed the specification and design of a dual RS449 high speed communications channel card for a new video teleconference CODEC.

- Designed the digital image filter controller using FPGAs and a new ASIC chip. This digital filter was used on new digital image display boards to be used in image compression products.

0-5 years of experience

Designed, 8 of 12 PCB’s used in the Low Altitude Navigation and Targeting Infrared Night System (“LANTIRN”) digital scan converter.

- Incorporated 2 dimensional digital filter and developed new line interpolation algorithms.

- F16 software integration at general dynamics and Flight test at Edwards AFB.

- Designed circuit using programmable logic devices which decode optical pulses off the back of the scan mirror and calculate the mirror scan position address.

6-10 years of experience

Designed DSP and Image Processing PCBs for GE’s first premium Ultrasound machine, the LogIQ700.

- Front End Equalization Board. IQ data filtering and B-Mode image correction for depth effects.

- Back End CINE Board. Image storage and processing with programmable replay capabilities. Supported first 3D images from a 2D machine. Designed a gate array image controller.

- Initiated and performed HALT and HASS design integrity testing at the system and rack level for the Ultrasound business. Improved MTBF and design quality of several PCB designs.

0-5 years of experience

Avionics Systems Engineer/Senior Digital Design Engineer

- Multipurpose Bomb Rack (BRU-69/A) RFP Technical Volume. Provide multiple weapon interfaces electronic solution. Successfully completed the RFP electronic technical package.

- Rail Launcher (M299) RFP Technical solution. Provided multiple weapon interfaces electronic architecture. Successfully completed the RFP electronic solution.

- Produced electronic technical solution for a Bomb Rack Pneumatic deployment system. Conceptualized bomb rack electronic solution with multiple weapon interfaces and develop requirement specifications.

- Aerial Refueling System trade studies and technical assessment for adaptation to an UAV aerial refueling.

- Oxygen System Meter. Generated requirements document and redesigned the oxygen meter controller board.

- Military Aircraft Electrical Interfaces (F/A-18, F-35, F-22, V-22), Weapon Interfaces (Hellfire, JDAM, JAGM, TALD, SDB, JMMI, and MMSI), Military Standards (MIL-STD-1553, MIL-STD-1760E, EBR-1553, and Miniature Munitions Store Interface) and schematic capture (OrCAD).

0-5 years of experience

Tested and designed embedded systems for SATA applications with Xilinx and Altera FPGAs.

- Developed and integrated Firmware for SATA AHCI protocol.

- Integrated Linux drivers for the SATA peripheral core with the Altera and Xilinx SoC FPGAs.

- Supported customers with integration of Intellectual Property.

- Created internal and external documentation on projects.

6-10 years of experience

Architected, implemented, and tested software-defined radio (SDR) applications in GSM, UMTS, and CDMA2K. Designed DSP functions in receiver, such as synchronization, descrambling, de-interleaving, decoding, filtering, CRC correction, symbol tracking, frequency correction, etc.

- Created MATLAB and Simulink simulation models, built HDL models, and architected system design for performance and speed.

- Generated System on Chip (SoC) applications with embedded processors, such as NIOS-II, and tested functionality by writing automated test scripts and performing lab and field tests.

- Designed complete communication systems by providing interface to all external devices on hardware platform, such as PCIe bus, ADC, DAC, DDR, OMAP, Ethernet MAC, Flash, SPI, UART, I2C, etc.

- Provided feedback on PCB design based on system requirements and design architecture considerations.

- Led customer meetings, conducted project status presentations, provided technical advice to project team, coordinated with outside contractors on project tasks, and mentored new hires.

0-5 years of experience

Design of Image Scanner ASIC with customer (HP) design team. Designed (verilog) and verified interface logic between USB core and scanner backend.

- Wrote functional specification for USB core.

- Inserted internal scan, executed ATPG, created test vectors for ASIC fault coverage.

- Provided consultation for customer design team on scan, synthesis, simulation, USB technology, and general LSI digital library requirements.

- Design of SSA Disk Drive Controller ASIC. Designed (verilog) and verified interface logic between SSA core and disk controller backend. Integrated SSA protocol engine. Wrote functional specification.

0-5 years of experience

Designed a plug-in PCB of I/O Channels for a Millimeter Wave Radio that enabled systems to be re-configured after final assembly.

- Managed development projects of three ASIC’s that produced large cost reductions.

- Took ownership of digital hardware product for Engineering and fully supported it in Manufacturing by writing and implementing ECO’s that fixed or improved problems.

- Analyzed faulty power supply performance, selected its replacement and performed final qualification for its release.

0-5 years of experience

Designed and created firmware modules to work within an existing system

- Wrote new modules and edited existing modules in VHDL

- Developed test scripts in Python and utilized these scripts to quickly test multiple units

- Debug firmware and software by testing units, isolating problems, and fixing bugs

- Designed fixtures to test units using various equipment such as oscilloscopes, spectrum analyzers, and pulse generators

- Performed individual tasks while functioning as a member of a team

- Responsible for secrecy of projects

0-5 years of experience

Performed wide range of engineering functions for a fast paced RFID Semiconductor Company.

- Responsible for cross-functional team support and external supplier interface.

- Designed and tested electrical validation plans using specification analysis.

- Implemented engineering tools for complex electrical designs including RFID and memory chips.

- Provided technical expertise, quality testing, benchmark studies, backend research and troubleshooting of complex problems.

- Performed external vendor relation for purchasing and maintaining CAD tools.

0-5 years of experience

Responsible for the architecture, implementation, and silicon performance of core state machine for Monza tag chips. Owned all aspects of design throughout product life cycle including conformance to industry specifications, synthesis, custom CMOS logic, verification, and high-volume production.

- Ultra-low power CMOS and novel digital architecture, first Class1 Gen2 tag in the world.

- Billions of chips produced with extremely high yield, 10-year reign with #1 market share.

- Adopted by industry as “gold standard” for conformance testing.

- Created FPGA-based tag emulator to allow rapid experimentation of new features.

0-5 years of experience

Responsible for design and testing of electronic devices related to liquid level sensing industry.

- Designed and tested 1MHz/5MHz R.F. amplifier board for sludge density measurement product using high gain, high frequency op-ampl., resulting in reduced cost, smaller size and superior performance.

- Assisted in redesign of continuous liquid level sensing product utilizing LSTTL and HCMOS digital logic families in circuitry to realize state-of-the-art performance in speed/power.

- Conceptualized, designed, built and tested product based on Fourier analysis concepts to obtain high frequency sine waves from digital square wave oscillators, resulting in less expensive/more compact product.

6-10 years of experience

Designed and developed Flash Management Units (FMUs) for a wide variety of automotive, commercial, and industrial SoCs containing on-chip Flash non-volatile memory arrays. FMU designs incorporated complex state machines and ARM microprocessors. Design responsibilities were primarily digital logic design and verification and assembly-level and C firmware development.

- Developed novel approaches for the creation of baseline hardware designs which were easily reconfigured, ensuring rapid delivery of many derivative products.

- Created a program ‘Swap’ feature which was a game-changer for customers needing easy, in-the-field, low-downtime, application code updates.

- Re-architected the assembly code for a major product family which greatly reduced engineering time-to-market.

- Led the design team’s development and analysis of emerging industry standards for IC power modeling (CPF), for best-in-class low-power performance.

- Directed the team’s analysis and solution of complex clock-domain crossing design issues when multiple asynchronous, local oscillators were employed.

- Generated and reviewed many pre-layout gate count, STA, Lint, and testability reports to provide high-quality handoffs ensuring problem-free system integration.

- Implemented and documented proprietary hardware access schemes for software IP protection.

- Worked with SoC architects to redefine and redesign high-speed embedded Flash read interfaces.

- Designed ARM Cortex AHB slave bus interfaces and line buffers to significantly improve system throughput.

- Developed the functional requirements and designed the hardware and firmware for all-new memory content verification functions used by end customers and factory test.

0-5 years of experience

Lead Digital Design Engineer transitioning DARPA Trust in Integrated Circuits program to AFRL.

- Applied custom and commercial tools to prove logical equivalency between suspect ICs and golden designs and detect if malicious logic was inserted at the netlist and GDSII levels.

- Researched destructive and non-destructive techniques to extract the layout and functionality of packaged circuits.

- Performed gap analysis on DARPA delivered tools and formulated a research plan to address gaps.

10+ years of experience

Responsible for the design of prototype and support electronics for inertial navigation instruments

- Designed 16-bit A/D instrumentation board used in assisting development of enhanced accelerometer design

- Designed accelerometer interface for Gravity Measurement systems using R65/11 micro controller

- Responsible for field service repair and maintenance of shipboard R&D Gravity Gradient Sensor System. The system was credited with very little downtime due to immediate repair.

0-5 years of experience

Responsibilities included electronic design and integration of various phases of product development.

- Served as lead developer/designer of an FPGA to be used in a digital cinema projector.

- Developed the design specification detailing the timing and image data stream architecture.

- Coded the design in VHDL, performed simulations and timing checks to ensure proper functionality.

- Worked with a mechanical/optical team to integrate the electronics to a mock projector.

6-10 years of experience

Conceptualized, designed, and developed electronics printed circuit boards and FPGAs. Utilized Cadence schematic entry, FPGA development hardware and software kits, VHDL, PCI, UART.

- Translated customer needs and requirements into technical requirement specifications. Documented designs and oversaw release of specifications to ensure that customer requirements were met. Performed hardware and software system integration and testing.

- Designed, built, and tested circuit boards that interface with existing processor board to support new customer’s GPS receiver board.

- Designed and developed prototype boards to support testing of new hardware designs.

6-10 years of experience

Designed microprocessors cards (68040, 601 RISK, & 86186), Ethernet, SCSI, and RS-232 serial ports. This includes schematic capture using Mentor Graphics and debugging in the lab. I have also verified code, and written and tested functions to check out sections of boards.

- Part of team designing, testing, debugging, and reworking a digital filter. Did extensive simulation and debugging of complicated sections of the board. Was heavily involved in bringing up the first 6 prototype boards. While first board was being extensively tested, by another engineer, brought up boards 2 through 6.

- Designed an embedded controller board with a high speed PCI data communications section.

- Designed a high speed data acquisition board.

0-5 years of experience

Provided engineering services, hardware and software) for the ALQ-131 Independent Test and Verification, Mission Data Generator, and Electronic Warfare Operational Test Systems contracts.

- Designed a digital interface between a VAX 11/780 host computer to PDP 11/34 computer and ALQ-131 EW pod for the Mission Data Generator System.

- Integrated and tested the field demonstration prototype of the Mission Data Generator system.

- Designed a Pulse Conversion Subsystem for the Electronic Warfare Operational Test System.

0-5 years of experience

Designed ‘Set Top Box’ digital decoder for the video industry.

- The design involved the use of DSP’s (Analog Devices ADSP2105), Microprocessors (Intel’s 80C152),

- FPGA’s (Xilinx), EPLD’s (AMD).

- The designs realized include ‘Reed Solomon’ error correction, scrambling de-scrambling and ABBE (adaptive base band equalizer), digital (FIR), and analog filters.

- Wrote test code using Microsoft C/C++ 7.0 compiler. Wrote all DSP (assembly) and Microprocessors (assembly& C) code.

- Designs encompass all aspects including frequency synthesizers (PLL’s).

- Some boards were designed to interface with PC’s via the EISA/ISA bus.

0-5 years of experience

Worked as a digital design and test engineer on the Large Hadron Collider (LHC) experiment with the aim to prove the existence of the Higgs Boson

- Ddeveloped the specifications, designed and tested High Speed Data Acquisition and Complex Processing Circuits on Xilinx Virtex2Pro FPGAs on a VME 9U Data Acquisition Board (Data Concentrator Card)

- Altogether, responsible for designing, testing and maintaining firmware for about 540 Xilinx Virtex2Pro FPGAs spread over 60 DAQ Boards

- Developed JTAG Test Benches by Merging net lists for 1 Motherboard and 5 daughter-boards for simultaneous testing and production testing of 1500 PCBs

0-5 years of experience

Developed and verified RTL in Verilog to implement glue logic for a new generation communication 4 channel ATM/PPP chip with integrated DS3/E3/STS-1 framing controller.

- Developed testcases to check access to the registers, to check datapath of the chip in ATM mode with direct mapping and E3/DS3 framing. Also ran regressions, debugged, and helped resolve a silicon issue.

- Developed interrupt model to check interrupt registers for each block of the chip and to verify the functionality of the chip during interrupts.

- Developed Perl scripts to help automate the design flow. Developed scripts to check if all testcases were run in the regression, to check the results of the regression, to generate standard files related to each testcase, to help instantiate a module.

- Evaluated Spyglass (Verilog LINT checker) and Debussy (RTL Debug tool).

0-5 years of experience

Designed, developed and released to manufacturing VoiceXtenger(TM) for Single Line Wireless Communication based on Spread Spectrum Technology. Altera FLEX 8000 FPGA, Mux Plus II and OrCAD design tools were utilized.

- Designed, developed, and released to manufacturing XILINX FPGAs XC3000 and XC5200 families for high speed wireless data communication modems and phone applications.

- Designed and developed test fixture subsystem for QPSK modem and local microprocessor. Design utilized high-speed sequential and parallel circuits, interfacing to an on-board microprocessor, FIR filters. Utilized Verilog HDL, SignalScan, Synplicity and Altera tools.

- IBM, San Francisco, CA .

0-5 years of experience

- Designed and developed a board which allowed existing PBX to support the Microsoft Windows telephony application programming interface (TAPI).

- Implemented logic design and synthesis using Altera’s MAXPLUS2 development tool for the Max 7000 and Flex 8000 products.

- Coded and debugged firmware in assembly language for 8051 microprocessor.

- Responsible for product design and production support, including the generation of all documentation and production test procedures.

0-5 years of experience

- Developed IP reference designs including PCI to DDR interface, Marvell Xscale to MMC/SD/SDIO interface, and Marvell PXA3xx to PXA2xx bridge.

- Provided customer service support for Quicklogic products to existing customers

- Wrote and reviewed product specifications and application notes

0-5 years of experience

FPGA Design Team

- Performed design conversion from Xilinx Spartan IIE FPGA to Actel ProASIC3 FPGA for Audio over Ethernet application.

- Modified Verilog RTL Design from a 32×32 channel design to an 8×8 channel design.

- Performed functional verification using ModelSim simulator.

0-5 years of experience

Responsible for ASIC design for a cordless multi-line phone system

- Developed TDMA multi-link protocol for frequency hopping technology in 900 MHz ISM band that resulted in four (4) patents

- Led a team to define an ASIC design process for ISO-9000 certification

- Transferred wireless technology from research to development for the 900 MHz ISM band phone

- Defined hardware requirements for 900 MHz receiver subsystem.

- Performed prototype emulation for ASIC design using Synopsys VHDL synthesis, and Mentor Graphics schematic capture and simulation tools

6-10 years of experience

Analyze fielded failure units to root cause, determine corrective action, report results to Failure Review Board and manage the daily operations of the Failure Analysis Lab

- Created reporting and tracking Infrastructure database for Motorola’s Failure Analysis Lab (FAL) to track DUTs, recording unit SN details, visible damage, origination, symptom, failure disposition, component level details and remediation. Tracking system implemented company-wide.

- Provided using Excel database, statistical analysis on 1,000 units over 3-year period to functional groups in “real” time eliminating lag time to assess/identify endemic issues.

- Diagnosed fielded failures to root cause and issued corrective action to organizational units saving $972K in yearly repair costs, $129K (2010) in defective vendor chargebacks, and prevented a recall / refit note on 500K shipped units.

- Monitored by editing/returning for requalification performance of vendors’ samples and identified improvements to mitigate the failure mode by discussing analyses with vender representatives.

- Advanced user of X-Ray: Glenbrook Technologies Jewel Box 70T, Endoscope: EasyBraid VIP-1000, Thermal Imager: Fluke Ti32, Optical Spectroscope: StellarNet Blue-Wave NIR50, Optical Radiometer: PhotoResearch PR-650, Thermal Chamber: Thermotron SM-8C MiniMax, ESD Testing: KeyTek ESD1, and BGA Machine: AirVac DRS25

- Reduced test time by 50% and an agreement of results within 5 feet which improved repeatability and test with design / standardization of test environment for Set Top Box 360 degree angular IR reception distance.

- Developed HW portion of PMR documents and translated into PFS requirements for the Aegis Portable Media Player. Responsible for ESM facility assessment.

- Coordinated team of 12 engineers, providing comprehensive Block Diagrams, Test Plans, resource assignment and Design Verification Analysis for the DCH6400 Advanced Set Top Box.

- Assessed impact of newly designed Lens and bezel in ASTB using Minitab First Principles Modeling, DOE, and Two Sample T-Test. Verified Cp/Cpk targets were within guidelines for Six Sigma design by using Crystal Ball Monte Carlo assessment.

- Received DFSS Green Belt Certification.

6-10 years of experience

Implemented designs for avionics applications which utilizes 89C51 Micro-Controller and interfaces via I2C, SPI, ARINC 429, and RS-232.

- Familiar with DO-254 design requirements standard.

- Carry out board design from schematic level to fabricate/assembly.

- Perform system integration test.

- Written design documents for projects under taken.

- Provided support to existing designs (repair /troubleshoot).

- Competent at using surface mount station, experienced with Data I/O programming station.

0-5 years of experience

Designed 68000 and 68020 computer system for high-speed data acquisition and image processing on semiconductor test equipment.

- Designed human-machine interface (HMI) for precision X/Y stage positioner. Trackball interface allowed users to position stage in one-micron steps or slew the full six-inch travel in seconds

- Designed software drivers for various HMI applications

- Worked with industrial designers on how to integrate HMI into product line

0-5 years of experience

- One of the projects required development of embedded firmware on a Motorola DSP56803 platform for state-of-the-art smart site-configurable digital and analog modules. It involved implementation of real-time automatic-gain-control and advanced signal-processing routines for the video modules, laser driver and control algorithms for the optical transmitter and photodiode power-monitoring routines for the optical receiver. Finally, site configuration and status monitoring of the entire unit was implemented using an SNMP based management system over CAN bus.

- System-architecture (hardware and software) development for a unique OEM solution for SBC Ameritech was the focus of a second project. It required conversion of two NTSC video signals with associated audio into a single DS3 transmission signal or vice versa. The DSP firmware implementation for the compression/decompression of the video signals (based on a unique wavelet-compression algorithm) and MPEG2 protocol packetization was done on an ADSP-2185 platform with ADSP218X EZ-ICE emulator using both assembly and higher-level language (C). In addition, generation of the asynchronous multiplexing and demultiplexing of the video and audio signals over a DS3 line was implemented on a Xilinx Spartan2 FPGA using VHDL.

- A third project led to the firmware development on Microchip PIC16F876 platform for one of the first industrial MEMS based photonic-switch router (PSR) for pure all optical routing of high-bandwidth network like Internet traffic for LuxCore Networks. The main modules developed for this router were a filter Mux card, Wavelength Converter Card, MEMS switch card and an Optical controller card-all of them using state-of-the-art MEMS based photonic devices.

- Firmware development of a CATV broadband fiber-optic system for transmission up to 110 channels over a single fiber was the focus of a fourth project. The system, developed on a Microchip PIC16F876 platform, enabled remote monitoring of system critical parameters such as total RF input power, optical input power, laser operating temperature, and power supply voltage. A further project need was development of a GUI menu driven management system that allowed a plug-and-play addressing of each unit over a RS-485 based daisy-chained network.

0-5 years of experience

Bore Hazard Detection – Image capture and pixel scanner

- Designed and debugged 8 layer PCB with ARM7, FPGA, SRAM, FLASH, and USB.

- Design of Digital Filter for Sigma Delta Converter. Wrote RTL code for 24 tap FIR filter in Verilog. Performed decimation and noise shaping.

- Designed FPGA to control high speed X-Ray Detector array.

- Designed and debugged 10 layer PCB with PCI interface, FPGA, 8b/10b SERDES chip.

0-5 years of experience

Develop new intellectual property and product concepts as part of the Research & Development team. Design digital portions of wireless data products as part of the product development team.

- Design and develop hardware and logic for non-RF portions of next generation wireless CDPD modem. Reduce power consumption, size, and cost.

- Implement data recovery logic and portions of the CDPD MAC layer in a Xilinx Spartan-II FPGA using VHDL for CDPD modem design.

- Schematic capture and multilayer board design using PADs PowerLogic and PowerPCB.

- Develop a new proprietary low-cost and low-power RF product, including protocol design, hardware, and embedded firmware for TI MSP430 microcontroller implementation of protocol.

- Design and develop a proprietary 8-bit processor and instruction set for use in FPGAs.

- Develop firmware for Atmel AVR and Microchip PIC microcontrollers for research projects.

- Other IP developed for research includes DTS spread-spectrum spreading schemes in a FPGA, then in a microcontroller using C and assembly. Development of GMSK (Gaussian Minimum Shift Keying) direct synthesis and FIR filters in a FPGA. SciLab used for mathematical development.

0-5 years of experience

- Push-Pull Stage LED Driver: Improved accuracy and efficiency in generation of register file (RTL) and associated validation/verification files by automating using PERL script. Designed Memory Controller for interfacing digital design with OTP. Setup and debugged mixed signal simulation to help verify key functional aspects of the Chip. Validated calibration and OTP programming process for fabricated chip.

- Boost LED Driver: Designed analog calibration modules to help correct variation of analog parameters. Created Verilog models of mixed signal components for digital and scan simulations.

- Single stage LED Driver: Executed Physical Design flow (Synthesis, P&R, Extraction and Pattern Generation) to achieve area reduction. Led the verification effort to ensure 100% Coverage across Simulation and Emulation phases. Maintained and added features for regression scripts.

- Metering Platform: Designed/Verified Cocktail March BIST algorithm for Data RAM. Implemented serial testing module for Flash memory.

- High Voltage Power Train: Implemented mixed signal verification for multi-chip module involving analog, digital and firmware.

- Pet Project: Conceptualized and implemented mixed signal simulation flow involving models of on-chip analog circuitry and schematics of power train for easy system level validation using general purpose microprocessor core and firmware.

0-5 years of experience

- Managed a design from the conceptual stage to a finished deliverable product.

- Generated a product contract and product specification

- Schematic capture, PC board layout, testing, and debugging

- Provided the necessary technical information for a product manual

- Coordinate efforts with Manufacturing Engineering to obtain a manufacturable product

- Responsible for the final check-out and release of a product

0-5 years of experience

Worked on a high-efficiency, low cost, mixed-signal, system-on-chip product that implements a back-emf based, sensorless, pseudo-sinusoidal control algorithm for BLDC motors used in air-conditioners and pumps

- Primarily responsible for the IC definition, system validation, digital architecture, RTL implementation, synthesis, verification and successful tapeout of this mixed-signal SoC

- Performed all relevant back-end tasks (RTL to GDS) in this project and successfully taped-out in Mar’08.

- Extremely adept with a variety of EDA tools through out the entire mixed-signal flow – system modeling & validation, mixed-signal system simulation, RTL simulation, synthesis, DFT, floor-planning, power routing, place & route, ATPG, STA, DRC & LVS, etc

- Improved acoustic noise, stability and efficiency of the system by using a variety of digital filtering, error correction and data recovery techniques

0-5 years of experience

Worked on SOC Interfaces and Controllers Design, Gained knowledge on these high speed interfaces to help debug the existing failing tests and to develop new tests .

- RTL Design and Formal Verification for a flash memory controller with AHB interface.

- Formal Verification of PCI Interface on PCI-IPB bus with Verilog HDL.

- RTL Design and Formal Verification of a DMA Controller with five channel Individual Programming.

- Validation of the Timing and Signaling boards with Tektronix Logic Analyzers.

0-5 years of experience

Design embedded systems using OrCAD Capture, Layout and Allegro Layout

- Project management: Seeing projects from “cradle” to “grave”

- Research parts and designs to incorporate into products

- USB, RS-232, SPI, I2C, UART

- Design ARM7 based embedded systems

- Develop firmware for embedded systems using C

- Development of user interfaces with C++/Java

6-10 years of experience

- Led the hardware design and development of the biggest project GMS division has done, this M2T transmitter design was used in a government bid worth $100 Million.

- Designed the M2T from concept, high-level design, detailed circuit design, schematic development, lead a review team, and prototype integration and test. Creating the first high definition wireless C-OFDN HD video TX/RX.

- Responsible for designing of high speed low power, battery operated wireless products having the device operate up to 8 hours on one battery.

- Board level experience with high speed digital, baseband/analog circuits. Including design validation and integration into other products. Creating high quality audio video products.

- Designed complex digital cards and products supporting high speed audio/video processing and wireless and wired communication. Creating products that were sold even on the first run.

- Utilized Code Composer Studio, AVR Studio, Chip Scope and other programs to debug hardware, firmware and software. Often learning new programs in just a few weeks.

- Responsible for managing documentation: Improved documentation by over 50% by adding a basic debug section on test procedures and more details to the test instructions.

- Utilized Xilinx ISE Design Suite to synthesize VHDL code and ModelSim for Simulation. These cards utilize commercial ASICs and FPGAs. Completely connecting FPGA’s with over 600 pins.

- Utilized EDA software to create Schematics and PCB’s often creating products that were sold even on the first run.

- Managed and performed engineering tasks of various projects on other GMS products successfully working with professionals in various fields.

6-10 years of experience

Architecture, requirements definition and design of variety of FPGA based wireless systems including CDMA, UMTS, WiMax 802.16, LTE data processing and transmission engines

- High Speed Fiber Interface for WiMax 802.16 wireless system data transmission engines

- UMTS wireless system data processing engine

- CDMA EVDO Forward Link Chip Rate signal processor

- Interface between CDMA EVDV processor and Baseband Card

- Module Channel Card for 3rd generation of CDMA Base Transceiver Station

- TSI interface between CHI (Concentration Highway Interface) Bus and Communication Processor’s TDM interfaces

- Interface between CDMA Processor and Baseband Card

10+ years of experience

- Developed large FPGAs and Complex Programmable Logic Devices (CPLDs) for Joint Tactical Radio System (JTRS) radio: CPLDs to control radio frequency (RF) front-end of multi-channel receiver; FPGAs to perform baseband filtering, RF control, network interfacing, memory interfacing, built-in test (BIT) and time distribution. Performed VHDL design, simulation, implementation and test. Worked closely with RF, software and systems teams to define requirements and to successfully integrate designs in lab.

- Led VHDL design and verification teams, developing modem infrastructure and other FPGA designs for transceivers on JTRS programs and an internal research and development (IRaD) program. Assisted in requirements development, architecture definition and design. Authored VHDL development plan to ensure VHDL was developed in a controlled fashion to minimize product defects. Managed teams through test and integration. Received Letter of Commendation for contribution to successful IRaD radio demonstrations.

- Worked with waveform supplier to integrate waveform with modem FPGA and perform lab testing. Completed ahead of schedule, allowing for early customer demo. Later managed team to update modem for waveform throughput optimization enhancements. Ported to multiple transceiver platforms for demos and customer delivery.

- Provided detailed historical estimates of VHDL design efforts for a proposal for software-defined radio program.

- Defined and conducted independent review process to mitigate risk of ASIC respin. Performed independent VHDL code review of design changes and managed 4-person verification team in functional simulation efforts to achieve 95% code coverage.

- Redesigned a parameter encoder ASIC (600k gates, 0.35u), performing VHDL updates to a largely schematic-based design. Worked with ASIC vendor through the back end process.

- Performed hardware testing and troubleshooting of multi-channel receiver modules in support of manufacturing test for JTRS customer delivery.

- Completed board schematics and performed hardware testing of a cryptographic processor module. Used PCI bus analyzer/exerciser and emulation probes on PowerPC processor. Simultaneously supported multiple test racks to allow parallel integration and test by hardware, software and stress test teams.

- Coordinated software and managed security needs for Environmental Qualification Testing of classified JTRS radio. Worked with systems, software, test and security teams to obtain required functionality and to implement security processes to enable testing at multiple sites.

0-5 years of experience

- Design lead on JTAG design, scan insertion, ATPG generation and recovered massive fault coverage loss.

- Published guidelines on ATE scan pattern import and OTP trimming procedures.

- First to bring scan simulation tools and environment to work on site.

- Owned mix-signal simulation and wrote critical AMS analog models.

- Owned verification test cases that involve analog heavy behavior.

0-5 years of experience

Member of the ASIC Vocoder group.

- Designed a hardware platform to test, evaluate, demo, develop, and debug the Vocoder code.

- Designed a full duplex demo board for the Q4400 Vocoder.

- Designed a board for the Vocoder ASIC to be used as a hardware test bench and as software development platform.

- Coded some utilities in Microsoft C.

0-5 years of experience

Developed multiple user, range finding, friendship bracelet.

- Developed spectrum scouring ad-hoc network to avoid interference from other devices operating in the 2.4 GHz band.

- Employed adaptive-ping rate algorithm to reduce power usage while paired devices were not collocated or moving

- Utilized extensive GPIO multiplexing on Micro Linear’s transceiver SDK to create fully-functioning prototype for American International Toy Fair trade show.

0-5 years of experience

RTL design in VHDL/Verilog for Xilinx FPGAs Virtex-7, Virtex-6, and Virtex-2.

- Created QDR/DDR memory interfaces, DSP functions, AXI-bus register files.

- Resolved FPGA timing issues through manual floorplanning in Xilinx planAhead.

- Used UVM in SystemVerilog to create testbenches for FPGA verification.

- Created makefiles to build and simulate FPGA projects.

- Created scripts in bash to automate and rigorously test FPGA functionality on hardware.

- Used MATLAB to interpret data and create test vectors for use in FPGA verification.

- Xilinx Vivado trained and certified by Doulos.

- Interfaced with hardware vendors to quickly resolve issues.

10+ years of experience

Product Design of Security and Wireless products.

- ASA5585 series Security appliances – System power and sequencer design

- CAT6K Line card wireless controller – System power and sequencer design

- Outdoor 802.11n Mesh Access Points – EMC, power, and PoE design.

- Outdoor 802.11g Access Point/Bridge – EMC, digital, PoE, and power design

- Indoor 802.11b/g Access Points – Digital and power design

- DOCSIS cable modem – RF, digital and power

- Signal Integrity and EMC responsibility on these Products

0-5 years of experience

Developed printed circuit boards (PCBs) and embedded systems in cross functional teams

- Chip-level design, board-level design, and embedded software

- Industries include medical devices, telecommunications, and industrial safety

- Mentored new engineers

0-5 years of experience

Job Function: Mixed signal design of concept test boards for future space missions.

- Conceive, design, fabricate and test ultra low torque ripple precision brushless DC motor control electronics for nanometer positioning. Design, construct and test 4-up life-test bed to showcase technology. Successful design was published in NASA Tech Briefs

- Analog circuit design, class D motor drivers.

- PSPICE modeling of circuits.

- Understand, and adapt existing FPGA PID motor control core to ultra low torque ripple, ultra high resolution sinusoidal BrushLess DC (BLDC) motor application.

- Design of coarse and fine stage rigid body motion control stages for positioning of mirrors and antennas over 10’s of centimeters to nanometer precision.

- Design of low-power Lead Magnesium Niobate (PMN) actuator drivers and milli-kelvin stability temperature controls for space based active mirror array telescope applications. Interface with Hall sensors and 5 nm interferometric encoder.

- Mixed signal design of Motor Control and Sensor electronics boards used throughout Mars Science Laboratory (MSL).

- Linear Variable Differential Transformer (LVDT), Interface electronics to Resolvers and interferometric quadrature encoders.

- All designs for space applications involving high reliability, radiation hard components, FMEA

0-5 years of experience

Vector co-processor – ASIC design and implementation, that include design specification, RTL coding, synthesis, LEC, simulation verification, of a 16-bit vector pipeline co-processor for an embedded processing system in 55 nm process and clock speed of 232 MHz. The co-processor is capable of 232 MFLOPS, and is well-suited for implementing various digital signal processing algorithms.

- Instruction cache – design and implementation of an 8 K words 2-way set associative instruction cache.

- Serial test port – design and implementation of a serial test port with configurable width that connects the tester to the embedded processor

- ASIC prototyping of a touch controller with Xilinx Virtex-6 FPGA for hardware firmware/software co-development.

0-5 years of experience

- Responsible for the electrical design of Circuit Card Assemblies from concept to production

- Perform schematic capture utilizing Cadence Capture CIS

- Assist layout personnel in the PWB development process

- Develop firmware targeting Xilinx Virtex-6 and Spartan-6, and Altera Stratix-IV FPGA’s utilizing VHDL

- Develop VHDL Test Benches for verification of firmware designs

- Utilize Xilinx ML605 Development board for FPGA prototyping, including the use of Serial RapidIO (SRIO) for communication

- Familiarization with Anti-Tamper (AT) designs and FPGA Design Security